## Master's thesis

## **Development and Validation of Compact Models**

## for Si IGBTs and SiC MOSFETs in Power Elec-

## tronic Systems

Yifan Li

Limassol, December 2025

#### CYPRUS UNIVERSITY OF TECHNOLOGY

Faculty of Engineering and Technology

Department of Electrical Engineering, Computer Engineering, and Informatics

Master's thesis

# Development and Validation of Compact Models for Si IGBTs and SiC MOSFETs in Power Electronic Systems

Yifan Li

Supervisor

Neo Lophitis

Limassol, December 2025

**Approval Form**

Master's thesis

# Development and Validation of Compact Models for Si IGBTs and SiC MOSFETs in Power Electronic Systems

Presented by

Yifan Li

Supervisor: Neo Lophitis

Member of the committee: Committee member 1

Member of the committee: Committee member 2

Cyprus University of Technology Limassol, December 2025

## Copyrights

Copyright <sup>©</sup> 2025 Yifan Li

All rights reserved.

The approval of the dissertation by the Department of Electrical Engineering, Computer Engineering, and Informaticsdoes not necessarily imply the approval by the Department of the views of the writer.

### Acknowledgements

I would like to express my sincere gratitude to all my fellow students who accompanied me to Cyprus. Their unwavering support and assistance in both academic pursuits and daily life have been invaluable throughout this journey. The camaraderie and mutual encouragement we shared made the challenges of studying abroad more manageable.

My deepest appreciation goes to my supervisor, Dr. Neo Lophitis, for his exceptional guidance and mentorship. His kindness, patience, and profound knowledge have been instrumental in shaping my research skills. Under his thoughtful direction, I have learned not only the technical aspects of research but also the mindset and approach needed for scientific inquiry. His encouragement during difficult periods and constructive feedback have been crucial to the completion of this thesis.

I am also particularly grateful to my fellow research group members for their academic support and collaborative spirit. Our numerous discussions and exchange of ideas have significantly contributed to my understanding of the subject matter. The intellectual stimulation provided by these interactions has enhanced the quality of this research and fostered my growth as a researcher.

## ABSTRACT

This research addresses the challenges of accurately modeling power semiconductor devices, particularly the non-linear characteristics of IGBTs in the low-voltage region. A novel correction method based on transfer characteristics was developed and applied to both MOSFETs and IGBTs, revealing significant differences in their responses because of fundamental structural variations. The study found that while the correction method produced minimal improvements in MOSFET models (1. 83%), it dramatically improved the accuracy of the IGBT model in the low-voltage region: 12. 6% in MATLAB simulations and 21.7% in circuit simulators, with improvements up to 77.9% under specific gate voltage conditions. The research also compared NLM and Simple Derivative Implementation (SDI) capacitance modeling methods, demonstrating the superior numerical stability of NLM for complex device structures. These findings were validated through static characteristic fitting and double pulse testing. By bridging physics-oriented and mathematics-oriented modeling approaches, this research enhances the understanding of carrier transport mechanisms and conductivity modulation in different device structures, contributing to more accurate simulation tools for power electronics design. The improved models enable better prediction of device behavior in critical operating conditions, supporting advancements in applications from renewable energy to electric vehicles.

**Keywords**: Power semiconductor devices, IGBT modeling, transfer characteristics correction, junction capacitance modeling, wide-bandgap semiconductors

## **TABLE OF CONTENTS**

| A  | ABSTRACT v     |          |                                                     |     |

|----|----------------|----------|-----------------------------------------------------|-----|

| TA | ABLE           | OF CO    | DNTENTS                                             | vi  |

| LI | LIST OF TABLES |          |                                                     |     |

| LI | ST O           | F FIGU   | JRES                                                | X   |

| LI | ST O           | F ABB    | REVIATIONS                                          | xii |

| 1  | Intr           | oductio  | n                                                   | 1   |

|    | 1.1            | Aims     | and Objectives                                      | 1   |

|    | 1.2            | Resear   | rch Questions                                       | 1   |

|    | 1.3            | Contri   | bution                                              | 2   |

|    | 1.4            | Struct   | ure of the Thesis                                   | 2   |

|    | 1.5            | Summ     | ary                                                 | 3   |

| 2  | Lite           | rature ] | Review                                              | 4   |

|    | 2.1            | Functi   | ons of Semiconductor Device Models                  | 4   |

|    |                | 2.1.1    | Performance Prediction                              | 4   |

|    |                | 2.1.2    | Design Optimization                                 | 4   |

|    |                | 2.1.3    | Cost Reduction                                      | 4   |

|    | 2.2            | Basics   | of MOSFET and IGBT Modeling                         | 4   |

|    |                | 2.2.1    | Evolution of MOSFET Static Characteristics Modeling | 4   |

|    |                | 2.2.2    | Development of Power MOSFET Models                  | 5   |

|    |                | 2.2.3    | IGBT Static Modeling Methods                        | 5   |

|    |                | 2.2.4    | Sechyp Model and Characteristic Decomposition       | 6   |

|    |                | 2.2.5    | Structural Differences Between IGBT and MOSFET      | 6   |

|    | 2.3            | Major    | Challenges in Power Semiconductor Device Modeling   | 6   |

|    |                | 2.3.1    | Low-Voltage Region Modeling Challenges              | 6   |

|    |                | 2.3.2    | Carrier Transport Mechanisms                        | 7   |

|    |                | 2.3.3    | Carrier Transport Mechanisms                        | 7   |

|    |                | 2.3.4    | Dynamic and High-Power Application Challenges       | 7   |

|    |                | 2.3.5    | Parameter Extraction Challenges                     | 7   |

|    | 2.4            | Capac    | itance Modeling Methods and Implementation          | 8   |

|    |                | 2.4.1    | Capacitance Model Selection                         | 8   |

|    |      | 2.4.2 Nonlinear Mapping Method (NLM)                                            | 8  |

|----|------|---------------------------------------------------------------------------------|----|

|    |      | 2.4.3 Nonlinear Mapping Method (NLM) Implementation Approaches                  | 8  |

|    |      | 2.4.4 Simple Derivative Implementation Method (SDI)                             | 8  |

|    | 2.5  | Model Validation Methods                                                        | 9  |

|    |      | 2.5.1 Double Pulse Test Dynamic Characterization                                | 9  |

|    |      | 2.5.2 EMI and Switching Characteristics Correlation                             | 9  |

|    |      | 2.5.3 Parameter Extraction and Validation Methods                               | 9  |

|    | 2.6  | Research Directions and Opportunities                                           | 10 |

| 3  | МО   | SFET and IGBT Model Correction and Analysis                                     | 12 |

|    | 3.1  | Overview of Semiconductor Device Modeling Methods and Research Data Sources and |    |

|    |      | Experimental Design                                                             | 12 |

|    | 3.2  | Static and Dynamic Modeling of Semiconductor Devices                            | 13 |

|    |      | 3.2.1 Static Part of Semiconductor Device Model                                 | 13 |

|    |      | 3.2.2 Dynamic Part of Semiconductor Device Model                                | 22 |

|    |      | 3.2.3 Dynamic Detection Circuit and Switching Performance Evaluation            | 29 |

| 4  | Res  | ults and Analysis                                                               | 37 |

|    | 4.1  | Comparative Analysis and Verification of Semiconductor Device Static Models     | 37 |

|    |      | 4.1.1 MOSFET Correction Fitting Analysis                                        | 37 |

|    |      | 4.1.2 IGBT Model Fitting Analysis Based on Experimental Results                 | 38 |

|    |      | 4.1.3 Conclusion                                                                | 41 |

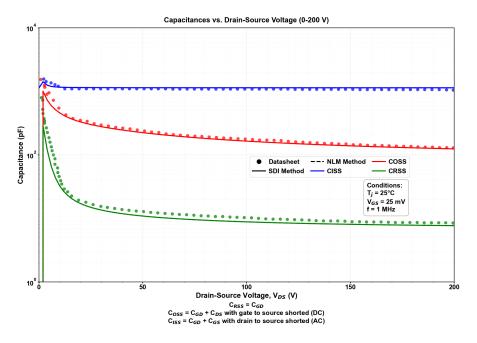

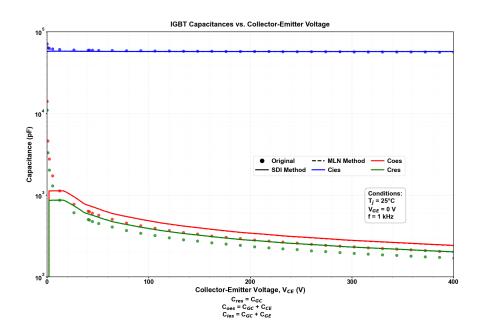

|    | 4.2  | Dynamic Capacitance Modeling Test Results                                       | 42 |

|    |      | 4.2.1 MOSFET and IGBT Junction Capacitance Model Verification and Analysis      | 42 |

|    | 4.3  | Double Pulse Test Results                                                       | 45 |

| 5  | Con  | clusion and Recommendations                                                     | 48 |

|    | 5.1  | Research Purpose and Key Findings                                               | 48 |

|    | 5.2  | Theoretical and Practical Implications                                          | 49 |

|    |      | 5.2.1 Theoretical Implications                                                  | 49 |

|    |      | 5.2.2 Practical Implications                                                    | 49 |

|    | 5.3  | Limitations of the Study                                                        | 50 |

|    | 5.4  | Recommendations for Future Research                                             | 50 |

|    | 5.5  | Summary                                                                         | 51 |

| BI | BLIC | OGRAPHY                                                                         | 53 |

| Al | PPEN | DICES                                                                           | 57 |

| I  | Circ | cuit Netlists                                                                   | 58 |

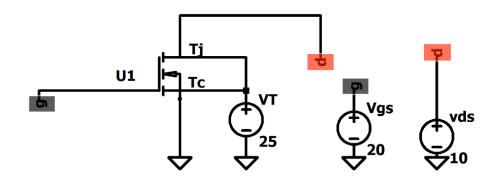

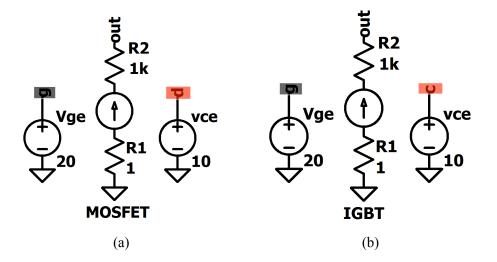

|    | I.1  | Static Model Test Circuits                                                      | 58 |

|    |      | I.1.1 MOSFET Static Model Test Circuits                                         | 58 |

|    |      | I.1.2       IGBT Static Model Test Circuits                                     | 59 |

|    | I.2  |                                                                                 | 60 |

|    |      |                                                                                 |    |

| I.2.1  | NLM Implementation Circuits        | 60                                      |

|--------|------------------------------------|-----------------------------------------|

| I.2.2  | SDI Implementation Circuits        | 61                                      |

| Double | Pulse Test Circuits                | 62                                      |

| I.3.1  | IGBT NLM Double Pulse Test Circuit | 62                                      |

| I.3.2  | IGBT SDI Double Pulse Test Circuit | 63                                      |

|        | I.2.2<br>Double<br>I.3.1           | I.2.1       NLM Implementation Circuits |

## LIST OF TABLES

| 3.1 | Time Parameter Evaluation Criteria                        | 35 |

|-----|-----------------------------------------------------------|----|

| 3.2 | Current and Voltage Change Rate Evaluation Criteria       | 35 |

| 3.3 | Turn-off Energy Loss Evaluation Criteria (600V/20A class) | 36 |

| 4.1 | Key Parameters for IGBT Model Correction                  | 40 |

## **LIST OF FIGURES**

| 3.1 | Comparison of IGBT and MOSFET structures. (a) The physical structure of IGBT. (b)                                                                                                                                                                                                                                                                                                                                                                          |          |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

|     | The equivalent circuit of IGBT. (c) Cross-sectional structure of a MOSFET that relies                                                                                                                                                                                                                                                                                                                                                                      |          |

|     | solely on majority carrier conduction.                                                                                                                                                                                                                                                                                                                                                                                                                     | 16       |

| 3.2 | C2M0080120D static test circuit                                                                                                                                                                                                                                                                                                                                                                                                                            | 21       |

| 3.3 | Application of static test for MOSFETs and IGBTs: (a) MOSFET static test circuit and                                                                                                                                                                                                                                                                                                                                                                       |          |

| 3.4 | (b) IGBT static test circuit                                                                                                                                                                                                                                                                                                                                                                                                                               | 21       |

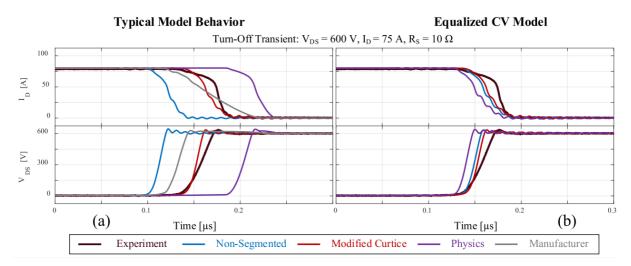

|     | els and experimental data for $R_g = 10 \Omega$ , $V_{DS} = 600 V$ , $I_D = 75A$ , $T_j = 25^{\circ}C$ . (a) behavior as published in the literature, and (b) altered to have identical capacitance mod-                                                                                                                                                                                                                                                   |          |

| 3.5 | els. [Reproduced from [1]]                                                                                                                                                                                                                                                                                                                                                                                                                                 | 23       |

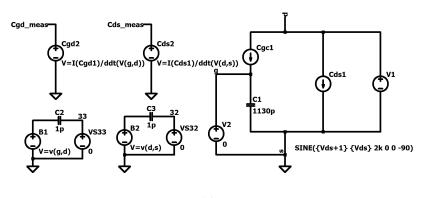

|     | itance test circuit using Nonlinear Mapping Method (NLM), (b) MOSFET capacitance<br>test circuit using Simple Derivative Implementation Method (SDI)                                                                                                                                                                                                                                                                                                       | 26       |

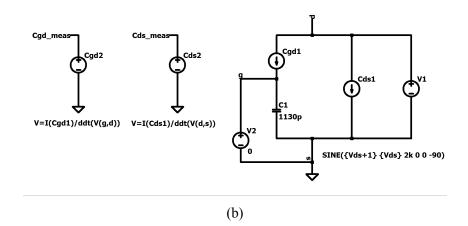

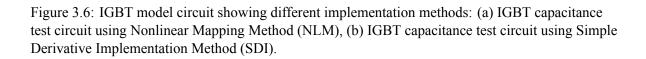

| 3.6 | IGBT model circuit showing different implementation methods: (a) IGBT capacitance test circuit using Nonlinear Mapping Method (NLM), (b) IGBT capacitance test circuit                                                                                                                                                                                                                                                                                     |          |

|     | using Simple Derivative Implementation Method (SDI).                                                                                                                                                                                                                                                                                                                                                                                                       | 27       |

| 3.7 | Double pulse test circuit in SPICE                                                                                                                                                                                                                                                                                                                                                                                                                         | 32       |

| 4.1 | Comparison of fitting effects between original and corrected MOSFET models: (a) Fit-<br>ting comparison in high voltage region (0-1000V), (b) fitting comparison in low voltage                                                                                                                                                                                                                                                                            |          |

|     | region (0-12.5V), and (c) legend for all curve representations.                                                                                                                                                                                                                                                                                                                                                                                            | 37       |

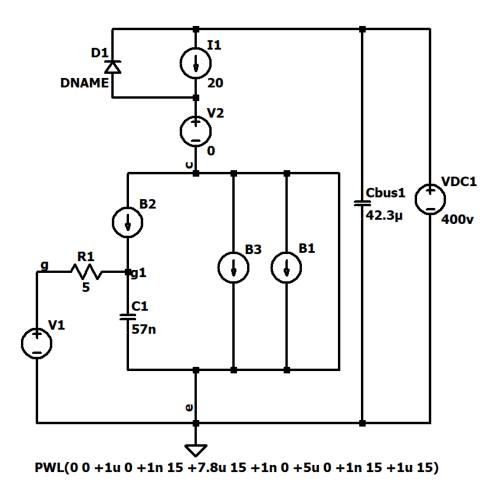

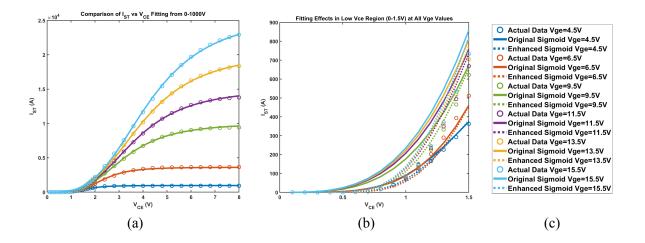

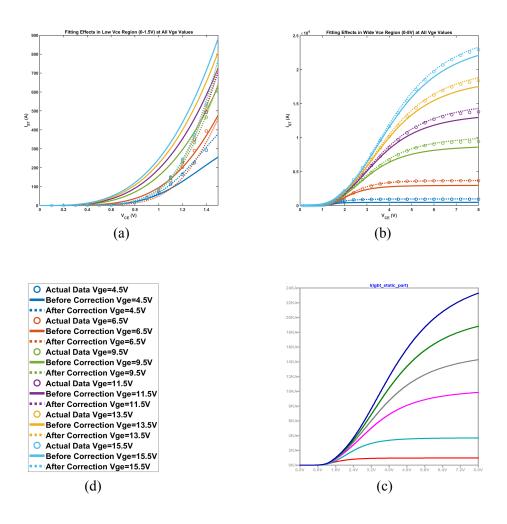

| 4.2 | MATLAB fitting results for IGBT model: (a) Low voltage region (0-1.5V) showing sig-<br>nificant improvement in fitting accuracy with the corrected model (dashed lines) com-<br>pared to the original model (solid lines), particularly at Vge=6.5V with 18.3% improve-<br>ment, (b) full voltage range showing overall performance where both models maintain<br>similar accuracy while the corrected model better captures the nonlinear characteristics |          |

|     | in the transition region, and (c) legend identifying different Vge values and model types.                                                                                                                                                                                                                                                                                                                                                                 | 39       |

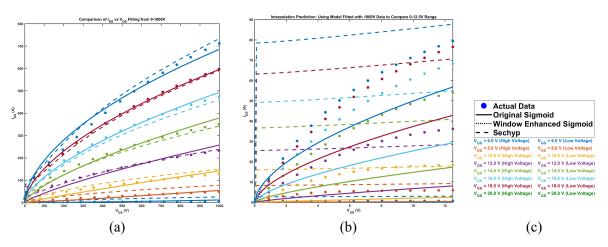

| 4.3 | Application analysis of IGBT fitting formula in circuit simulators: (a) Fitting effects in                                                                                                                                                                                                                                                                                                                                                                 |          |

|     | wide Vce region (0-8V) at various Vge values showing 19.6% average accuracy improve-                                                                                                                                                                                                                                                                                                                                                                       |          |

|     | ment, (b) fitting effects in low Vce region (0-1.5V) demonstrating significant enhance-                                                                                                                                                                                                                                                                                                                                                                    |          |

|     | ment up to 77.9% at Vge=4.5V, (c) circuit simulation waveform results showing dynamic                                                                                                                                                                                                                                                                                                                                                                      |          |

|     | performance, and (d) legend identifying different Vge values and model types from 1.5V to 15.5V.                                                                                                                                                                                                                                                                                                                                                           | 40       |

| 11  | MOSFET junction capacitance characteristics test results                                                                                                                                                                                                                                                                                                                                                                                                   | 40<br>42 |

| 4.4 |                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 42       |

| IGBT junction capacitance characteristics test results                                     | 43                                                                                                                                                                  |

|--------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

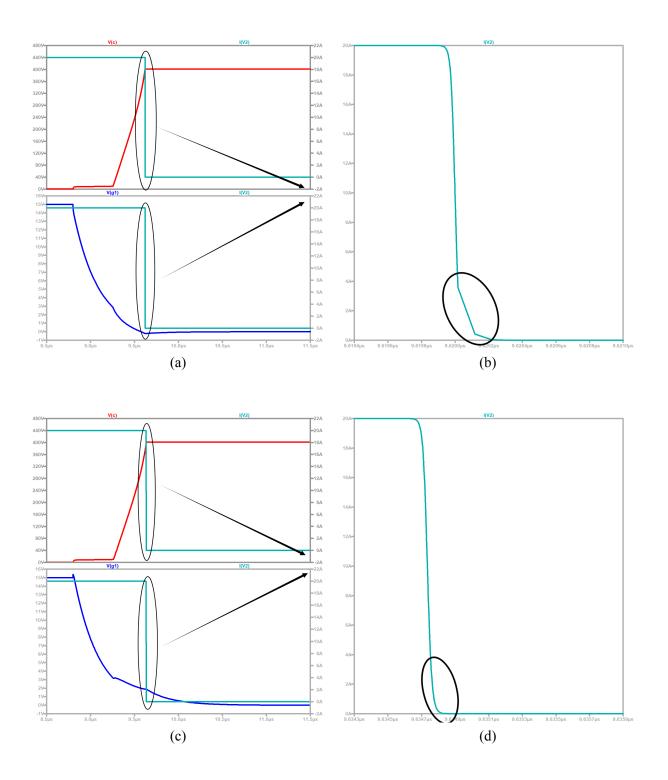

| Double pulse test results comparing NLM and SDI capacitance modeling methods: (a)          |                                                                                                                                                                     |

| switching waveform with NLM method during first turn-off, (b) NLM current falling          |                                                                                                                                                                     |

| edge detail showing smooth transitions, (c) switching waveform with SDI method during      |                                                                                                                                                                     |

| first turn-off, and (d) SDI current falling edge detail exhibiting steeper characteristics | 46                                                                                                                                                                  |

|                                                                                            | Double pulse test results comparing NLM and SDI capacitance modeling methods: (a) switching waveform with NLM method during first turn-off, (b) NLM current falling |

## LIST OF ABBREVIATIONS

| BJT    | Bipolar Junction Transistor                         |

|--------|-----------------------------------------------------|

| DPT    | Double Pulse Test                                   |

| EMI    | Electromagnetic Interference                        |

| GaN    | Gallium Nitride                                     |

| IGBT   | Insulated Gate Bipolar Transistor                   |

| LUT    | Look-Up Table                                       |

| MATLAB | Matrix Laboratory                                   |

| MOSFET | Metal-Oxide-Semiconductor Field-Effect Transistor   |

| NLM    | Nonlinear Mapping                                   |

| SDI    | Simple Derivative Implementation                    |

| SiC    | Silicon Carbide                                     |

| SPICE  | Simulation Program with Integrated Circuit Emphasis |

| TCAD   | Technology Computer-Aided Design                    |

## **1** Introduction

## 1.1 Aims and Objectives

The primary aim of this research is to create accurate and portable wide-bandgap semiconductor SPICE behavioral models. Power semiconductor devices, particularly MOSFETs and IGBTs, are fundamental components in modern power electronic systems, requiring precise modeling for system design and simulation. Despite significant progress in semiconductor device modeling, existing models still face challenges, especially in accurately representing the nonlinear characteristics in the low-voltage region of IGBTs.

The specific objectives of this research are:

- 1. To develop an improved modeling method that enhances the fitting accuracy of IGBT static characteristics in the low-voltage region while maintaining model simplicity and physical reasonableness.

- 2. To investigate and compare the structural differences between MOSFETs and IGBTs that lead to different responses to modeling corrections.

- 3. To evaluate different junction capacitance modeling methods (NLM and SDI) and their impacts on dynamic behavior prediction.

- 4. To verify the effectiveness of the proposed models through comprehensive simulation and analysis, including static characteristic fitting and double pulse tests.

- 5. To establish a scientific basis for selecting appropriate modeling strategies for different power semiconductor devices based on their physical structures.

### **1.2 Research Questions**

This research addresses several key questions in the field of power semiconductor device modeling:

- 1. How can the accuracy of IGBT models be improved in the low-voltage transition region while maintaining mathematical simplicity and physical reasonableness?

- 2. Why do MOSFETs and IGBTs respond differently to the same modeling correction methods, and what structural or physical mechanisms explain these differences?

- 3. How do carrier transport mechanisms and conductivity modulation in different device structures affect the effectiveness of model corrections?

- 4. What are the comparative advantages and limitations of different capacitance modeling methods (NLM vs. SDI) in representing dynamic behavior of power devices?

- 5. How can we effectively validate and quantify the improvements in model accuracy, particularly in critical operating regions?

By addressing these questions, this research aims to bridge the gap between physics-oriented and mathematicsoriented approaches to semiconductor device modeling, providing both theoretical insights and practical solutions for power electronics design.

## 1.3 Contribution

This research makes several significant contributions to the field of power semiconductor device modeling:

- 1. Development of a novel correction method based on transfer characteristics that significantly improves the fitting accuracy of IGBT models in the low-voltage region. The average fitting accuracy improved by 12.6% in the MATLAB environment and 21.7% in the circuit simulator, with improvements up to 77.9% under specific gate voltage conditions.

- 2. Quantitative analysis of the different responses of MOSFETs and IGBTs to the same correction method, revealing that IGBTs are significantly more sensitive to transfer characteristic corrections due to their composite structure and minority carrier injection mechanisms.

- 3. Comprehensive comparison of two major capacitance modeling methods (NLM and SDI), providing scientific basis for engineers to select the most appropriate implementation strategy for different application scenarios.

- 4. Verification of the physical reasonableness of the proposed corrections through analysis of the underlying carrier transport mechanisms and conductivity modulation processes in different device structures.

- 5. Development of a systematic testing framework combining static characteristic fitting analysis and dynamic double pulse testing, providing a robust validation methodology for power semiconductor device models.

These contributions not only enhance the accuracy of power semiconductor device models but also deepen the understanding of the physical mechanisms that underlie the different behaviors of MOSFETs and IGBTs, particularly in transition regions.

## 1.4 Structure of the Thesis

This thesis is organized into the following chapters:

**Chapter 1: Introduction** - Presents the aims and objectives, research questions, contributions, and overall structure of the thesis.

**Chapter 2: Literature Review** - Provides a comprehensive review of existing semiconductor device modeling methods, functions of models, challenges in modeling, and validation techniques. The chapter covers the evolution of MOSFET and IGBT modeling approaches, capacitance modeling methods, and identifies key research gaps.

**Chapter 3: MOSFET and IGBT Model Correction and Analysis -** Describes the methodology, including an overview of semiconductor device modeling approaches, the proposed correction method for the static part based on transfer characteristics, and the principles of different capacitance modeling methods for the dynamic part.

**Chapter 4: Results and Analysis -** Presents detailed experimental results, including comparative analysis of MOSFET and IGBT static model fitting, dynamic capacitance modeling test results, and double pulse test results. The chapter includes comprehensive analysis of the improvement effects and explains the physical mechanisms behind the observed differences.

**Chapter 5: Conclusions and Future Work -** Summarizes the key findings, discusses their implications for power electronics design, and suggests directions for future research.

Each chapter builds upon the previous ones to provide a coherent narrative of the research, from the identification of the problem to the development and validation of the solution.

## 1.5 Summary

This chapter has introduced research on the correction and analysis of MOSFET and IGBT models, highlighting the importance of accurate modeling of semiconductor devices for power electronic systems. The aims and objectives focus on developing improved models that address the limitations of existing approaches, particularly in the low-voltage region of IGBTs. The research questions probe the underlying physical mechanisms that explain different responses to model corrections across device types.

The contributions of this research include a novel correction method that significantly improves IGBT model accuracy in critical operating regions, comprehensive comparison of capacitance modeling methods, and deeper understanding of the physical differences between MOSFETs and IGBTs. The thesis structure outlines how these contributions are developed and presented across the subsequent chapters.

This research bridges the gap between modeling approaches oriented to physics and oriented to mathematics, providing both theoretical insights and practical solutions that can enhance the design and simulation of power electronic systems. By improving the accuracy of semiconductor device models, particularly in transition regions, this work contributes to the advancement of power electronics technology in applications ranging from renewable energy systems to electric vehicles and industrial automation.

## 2 Literature Review

### 2.1 Functions of Semiconductor Device Models

#### 2.1.1 Performance Prediction

Semiconductor models are crucial for predicting device behavior under different operating conditions, reducing the need for extensive physical testing. However, existing models face challenges in accuracy in high-temperature environments. Miyake et al. [2] pointed out that advanced IGBT models require comprehensive parameter extraction procedures that account for electrothermal characteristics to improve prediction accuracy in high-temperature scenarios. These limitations are particularly evident in high-power applications where heat dissipation and electrothermal coupling play key roles. Integrating temperature-sensitive parameters into compact models is essential to effectively address this gap.

#### 2.1.2 Design Optimization

Compact models facilitate circuit design optimization through efficient simulation of losses and thermal behavior. Koziel et al. [3] demonstrated that surrogate-based modeling and optimization techniques can accurately predict thermal and electrical losses, helping engineers refine designs while reducing computational costs. However, sensitivity to parameter variations in complex systems remains an area that has not been explored enough, limiting the robustness and adaptability of the model. For example, variations in gate drive resistance and load conditions often lead to switching losses that cannot be accurately predicted, which existing compact models fail to fully capture.

#### 2.1.3 Cost Reduction

Accurate modeling also contributes to a significant cost reduction by decreasing reliance on physical prototypes and failure testing. Islam et al. [4] developed artificial neural network models to predict the lifetime of semiconductor power devices under power cycle stress, which can reduce testing costs and accelerate development cycles, providing early insights into device reliability. When combined with external circuit test data, these AI-based models can further simplify the design process, reducing the costs associated with iterative hardware testing.

### 2.2 Basics of MOSFET and IGBT Modeling

#### 2.2.1 Evolution of MOSFET Static Characteristics Modeling

MOSFET static characteristics modeling has undergone significant evolution, evolving from early simplified models to modern complex compact models. The Level 1 model [5] was the first widely used MOSFET model, employing a regional approximation approach to describe the behavior of MOS transistors. Subsequently, the Level 2 model [6] introduced the effects of carrier mobility variations with the electric field, improving the model accuracy in short-channel devices. The BSIM series models [7, 8] further refined this direction, developing a more comprehensive framework that included the operation of the subthreshold region and the dependence of temperature.

The BSIM series models [7, 8], developed at UC Berkeley, represent a major advancement in MOS-FET modeling, progressively increasing the physical precision and parameter complexity from BSIM1 to BSIM4. Modern power MOSFET modeling faces unique challenges, particularly in describing nonlinear effects under high current and high voltage operating conditions. The MOSFET power model proposed by Hefner and Blackburn [9] pays special attention to accurately characterizing the variation of the resistance of the drain source (Rds \* Rds \*) with the drain current and temperature, which is critical for the prediction of power loss in high-frequency switching applications [9].

#### 2.2.2 Development of Power MOSFET Models

The development of power MOSFET models highlights the evolution from traditional silicon-based devices to emerging wide bandgap semiconductor technologies. Early power MOSFET models focused mainly on static I-V characteristics, such as the model proposed by Kraus and Mattausch [10] in 1998. Over time, the focus of the research shifted towards accurately capturing switching transients and dynamic behavior, as exemplified by the model developed by McNutt and Hefner [11] that included non-linear capacitance and temperature effects.

The emergence of wide-bandgap semiconductor technologies, particularly silicon carbide (SiC) and gallium nitride (GaN) devices, has greatly driven the development of power MOSFET models. The compact model proposed by Chen [12] for SiC MOSFETs specifically addresses their unique physical characteristics, including the structure of the conduction band and variations in carrier mobility with temperature and electric field. Kaisheng et al. [13] further investigated the impact of non-linear capacitance characteristics in wide-band-gap power devices on switching losses, providing key insights for high-frequency application modeling.

Modern power MOSFET models increasingly emphasize the balance between physical mechanisms and practicality, a trend that evolved from early work such as the physics-based semiconductor models by Kraus et al. [10]. These developments provide a theoretical foundation and practical background for the application of the transfer characteristic correction method in this research.

#### 2.2.3 IGBT Static Modeling Methods

Traditional IGBT static models belong to mathematically characteristic-oriented approaches inspired by physical properties, typically taking the following form:

$$I_{ST} = a - \frac{a}{1 + (V_{CE}/b)^c}$$

(2.1)

where  $I_{ST}$  is the collector current,  $V_{CE}$  is the collector-emitter voltage, and the parameters a, b, and c are functions related to the gate voltage  $V_{GE}$ . This model structure maintains mathematical simplicity while capturing the main physical characteristics of the IGBT, but it still faces challenges in a precise fitting in the low voltage region [14]. In circuit simulation environments, IGBTs are often implemented as hybrid equivalent circuits of N-channel MOSFETs and PNP bipolar transistors, reflecting the dual nature of their internal physical structure.

#### 2.2.4 Sechyp Model and Characteristic Decomposition

The Sechyp model adopts an approach to decomposing the characteristics of the device into the product of the transfer characteristics ( $F_{Trans}$ ) and the output characteristics ( $F_{Out}$ ), with its basic form as:

$$I_{DS} = F_{Trans}(V_{GS}) \cdot F_{Out}(V_{DS})$$

(2.2)

This decomposition method provides a new perspective for understanding power semiconductor device behavior, particularly advantageous in analyzing nonlinear characteristics in transition regions. Wiedemann et al. [15] developed a reduced order modelling approach for IGBT modules, achieving accurate characterization of junction temperature based on the on-state resistance. Perez et al. [16] developed a unified Si/SiC IGBT model based on this idea, achieving accurate characterization of both N-channel and P-channel devices. Mihalic et al. [17] further explored the implementation of this method in the SPICE environment, providing feasible solutions for engineering applications.

#### 2.2.5 Structural Differences Between IGBT and MOSFET

Understanding the basic structural differences between IGBT and MOSFET is crucial for accurate modeling. Huang et al. [18] demonstrated that IGBT employs a five-layer structure (emitter metal-N+ emitter region-P body region-N- drift region-P+ collector region-collector metal), while MOSFET uses a four-layer structure, resulting in significant differences in carrier transport mechanisms between the two. Baliga [19] described IGBT as having a dual modulation mechanism: on one hand, MOS channel control similar to MOSFET, and on the other hand, bipolar injection effects, with P+ collector region injecting minority carriers (holes) into the N drift region, reducing on-state resistance. This complex interaction between gate control and bipolar conduction explains why the same modeling methods may produce different effects between these two device types, especially in the transition region.

#### 2.3 Major Challenges in Power Semiconductor Device Modeling

#### 2.3.1 Low-Voltage Region Modeling Challenges

The nonlinear characteristics exhibited by power semiconductor devices in the low-voltage region have always been a challenge for accurate modeling.Liang et al. [20] proposed an improved analytical model, specifically optimized for predicting the switching performance of power semiconductor devices, significantly improving the modeling accuracy in critical operating regions. Verneau et al. [21] established a physics-based description method for low-voltage region conduction characteristics by analyzing the internal carrier distribution of power MOSFETs, providing a theoretical basis to accurately capture transition region characteristics. These studies indicate that low-voltage region modeling requires special mathematical treatment and physical understanding, especially for composite structure devices such as IGBTs, whose behavior in this region is more complex and requires comprehensive consideration of the coupling effects of multiple physical effects.

#### 2.3.2 Carrier Transport Mechanisms

#### 2.3.3 Carrier Transport Mechanisms

The fundamental differences in carrier transport mechanisms between MOSFETs and IGBTs create distinctly different modeling challenges. Baliga [22] in his authoritative work elaborates that MOSFETs rely solely on majority carrier (electron) conduction, with carrier type remaining unchanged as current flows from drain to source, while IGBTs involve a more complex dual-carrier transport mechanism. Trivedi and Shenai [23] described in detail the process in IGBTs where electrons flow from the N+ emitter region into the P body region to form an inversion layer (channel), then continue to flow through the N- drift region to reach the P+ collector region, while the P+ collector region injects minority carriers (holes) into the N drift region. This dual-carrier mechanism creates what Baliga [22] terms an "electron-hole plasma region," significantly altering the internal field distribution and making the mathematical description of current-voltage characteristics more complex. By injecting minority carriers (holes) from the collector p+ region into the n- drift region during forward conduction, the resistance of the n- drift region is considerably reduced Insulated-gate bipolar transistor - Wikipedia, but as Baliga [22] further explains, this advantage comes with additional complexity in switching behavior and device modeling.

#### 2.3.4 Dynamic and High-Power Application Challenges

Compact models often struggle to accurately predict dynamic responses such as di/dt and dv/dt, especially in extreme operating conditions where high injection levels and fast transition effects become prominent. Yang et al. [24] developed an improved behavioral model for high-voltage and high-power IGBT chips that addresses these challenges by incorporating nonlinear dynamic effects observed in extreme operating conditions. These challenges are further exacerbated by external circuit characteristics, including gate drive resistance, parasitic inductance, and load variations, which introduce additional complexity to device behavior. Jeong et al. [25] demonstrated that ANN-based compact models with expandable parameter extraction techniques for emerging transistors can improve dynamic parameter calibration, providing a way to enhance the accuracy and reliability of compact models in capturing real-world interactions and dynamic phenomena.

#### 2.3.5 Parameter Extraction Challenges

A key potential limitation of compact models lies in the complexity and time-consuming nature of parameter extraction, which is crucial for ensuring that models accurately reflect device behavior under different operating conditions. Compact models rely on parameters precisely calibrated through detailed analysis and iterative processes, often requiring extensive expertise and significant computational effort. For example, Navarro et al. [26] developed a sequential model parameter extraction technique for physics-based IGBT compact models, demonstrating the intricate steps required to properly characterize device behavior from various operating regions. This structural approach helps address the complexity challenge, but still requires expertise to implement effectively. This bottleneck is particularly problematic in fast-paced design environments where rapid prototyping, quick adaptation to new devices, and iterative testing are essential for maintaining competitiveness, highlighting the need for more efficient and automated parameter extraction methods.

#### 2.4 Capacitance Modeling Methods and Implementation

#### 2.4.1 Capacitance Model Selection

Selecting appropriate capacitance models for power semiconductor devices requires careful consideration of available data sources and computational efficiency. Nelson et al. [1] identified three main approaches in the literature: piecewise functions, continuous functions, and lookup tables (LUTs). While piecewise functions provide high fitting accuracy, they may introduce convergence problems. Continuous functions (such as arctangent, exponential, or hyperbolic tangent) ensure continuous differentiability but typically require numerous fitting parameters. As described by Mukunoki et al. [27], LUTs are popular due to their ability to be directly implemented from measurement data and their simplicity. For manufacturer datasheets providing limited characteristic points, continuous functions can achieve smooth interpolation between measurement points and facilitate parameter adjustment and sensitivity analysis [28]. In contrast, TCAD simulations typically generate a large number of data points already containing rich physical information and smoothness, making the LUT method applicable without the need to develop complex mathematical models [29].

#### 2.4.2 Nonlinear Mapping Method (NLM)

#### 2.4.3 Nonlinear Mapping Method (NLM) Implementation Approaches

The Nonlinear Mapping Method (NLM) has been implemented through several distinct approaches in semiconductor device simulation. Zeltser and Ben-Yaakov [30] proposed a comprehensive framework distinguishing between "total capacitance" ( $C_t(v) = Q/v$ ) and "local capacitance" ( $C_d(v) = dQ/dv$ ), implementing these concepts through a circuit-based technique using behavioral sources in SPICE. Their approach establishes a mathematical foundation by representing the nonlinear capacitance as  $Q = \int C_d(v) dv$  and applying symbolic differentiation to avoid numerical instabilities. Duan et al. [31], meanwhile, developed a specialized implementation for SiC power MOSFETs by modeling junction capacitances through piecewise equations aligned with measured device characteristics. Their method incorporates a voltage-dependent hybrid formulation where  $C_{gd}(v_{gd})$  and  $C_{gs}(v_{gs})$  are expressed as continuous functions derived from physics-based parameters and fitted to experimental data. This technique excels in predicting switching behavior under high-frequency operation by accurately capturing the dynamic response of depletion regions across the entire operating voltage range while maintaining superior numerical stability during complex circuit simulations.

#### 2.4.4 Simple Derivative Implementation Method (SDI)

The Simple Derivative Implementation Method (SDI) provides a direct and intuitive approach to simulating voltage-dependent capacitance, implementing the basic capacitor current equation  $I = C(v) \cdot dv/dt$ directly through a behavioral current source. Nelson et al. [1] analyzed two main variants: SDI1 for capacitance definition implementation (current source expression  $I = C_0 \cdot f_c(V_{1,2}) \cdot d/dt(V_{1,2})$ , where  $f_c$  is the voltage-dependent capacitance function) and SDI2 for charge definition implementation (simplified expression  $I = d/dt(f_q(V_{1,2}))$ , where  $f_q$  is the voltage-dependent charge function). While SDI provides conceptual simplicity and direct correspondence with physical definitions, Nelson's comparative analysis revealed a key limitation: its accuracy is highly dependent on the simulation time step selection. Their experiments clearly demonstrated that as the maximum time step decreases, the SDI prediction of damping characteristics gradually approaches the theoretically correct NLM prediction results, implying that extremely small simulation time steps need to be adopted to achieve acceptable accuracy, significantly increasing the computational burden.

### 2.5 Model Validation Methods

#### 2.5.1 Double Pulse Test Dynamic Characterization

The Double Pulse Test (DPT) has become the industry standard method for evaluating the switching characteristics and losses of power semiconductor devices. Meisser et al. [32] focused on integrated SiC MOSFET modules with ultra-low parasitic inductance design, providing a critical experimental foundation for noise-free ultra high speed switching evaluation. Hoene et al. [33] developed ultra-low-inductance power module designs specifically optimized for fast switching semiconductors, demonstrating significant improvements in switching performance and measurement accuracy. Nayak et al. [34] conducted a comprehensive comparative study of different loss measurement techniques for SiC MOS-FET based power converters, including double pulse test (DPT) and calorimetric methods for switching loss estimation.

#### 2.5.2 EMI and Switching Characteristics Correlation

Electromagnetic interference (EMI) assessment has become a key aspect of power device model validation, with capacitance modeling methods significantly influencing prediction accuracy. Wang et al. [35] demonstrated the decisive role of accurate capacitance models in predicting switching ringing and highfrequency noise, particularly studying how parasitic elements affect MOSFET switching performance. Haleem et al. [36] provided empirical evidence for capacitance model selection by comparing IGBT switching transient characteristics under different circuit topologies. Dwiza et al. [37] further verified the significant impact of capacitance models on system-level EMI performance through analytical approaches for common mode noise analysis in power converters. These studies collectively indicate that different capacitance implementation methods (NLM vs. SDI) may produce notably different results in EMI prediction, with NLM methods typically providing better curve smoothness and integral calculation stability, suitable for system-level simulation, while SDI methods may more accurately capture transient peak losses and critical state characteristics under edge operating conditions.

#### 2.5.3 Parameter Extraction and Validation Methods

#### 2.5.3.1 Curve Fitting Methods

Traditional methods, such as least squares optimization, are widely applied in parameter extraction due to their simplicity and computational efficiency. Navarro et al. [26] developed a sequential model parameter extraction technique for physics-based IGBT compact models that provides a systematic approach to calibrating parameters from different operating regions. This approach has proven effective for static and linear operating conditions. However, when applied to scenarios involving complex nonlinear behavior

or rapid dynamic transitions, these methods face significant challenges where assumptions of linearity and stability are broken, resulting in reduced accuracy and limited applicability in high-frequency or high-power systems.

#### 2.5.3.2 Machine Learning Methods

Machine learning offers powerful and robust alternatives for parameter extraction, especially in complex systems where traditional methods struggle to handle nonlinearity and dynamic behavior. Guo et al. [38] introduced an end-to-end AI-based automated process for semiconductor device parameter extraction that significantly reduces the need for manual adjustments while enhancing the model's ability to adapt to different operating conditions. These data-driven approaches are particularly effective at capturing complex relationships between variables, achieving higher accuracy and efficiency. However, they also present challenges such as the need for processing and optimization, which may limit their accessibility and scalability in certain design environments.

#### 2.5.3.3 Hybrid Methods and Future Automation

Hybrid methods combine the strengths of traditional approaches and machine learning techniques, achieving a balance between accuracy and computational efficiency. Duong et al. [39] demonstrated the effectiveness of physics-based compact model parameter extraction and optimization for GaN HEMTs, achieving significant improvements in dynamic and thermal modeling accuracy. Similarly, Miyake et al. [2] proposed a comprehensive parameter extraction procedure for advanced IGBT models with electrothermal features, employing iterative optimization particularly effective in calibrating dynamic parameters. These hybrid methods show tremendous potential in leveraging external circuit test data, which can further enhance parameter accuracy by capturing real-world interactions and conditions.

### 2.6 Research Directions and Opportunities

Based on this literature review, we can identify several key research directions closely related to the model developed in this paper:

- 1. **IGBT Low-Voltage Region Characteristic Modeling**: For the nonlinear behavior in the lowvoltage region caused by the complex physical structure of IGBTs, more accurate mathematical models and physical interpretations need to be developed, with special attention to the interaction between minority carrier injection and gate control.

- 2. Capacitance Modeling Method Optimization: Further explore the performance differences between NLM and SDI methods under different operating conditions, and develop improved implementation schemes that balance numerical stability and computational efficiency.

- 3. Extension of Transfer Characteristic Correction Method: Extend the transfer characteristic correction method developed in this research to other power semiconductor devices, studying its applicability and effectiveness in different device structures and material systems.

- 4. **Improvement of Model Validation Techniques**: Refine the double pulse test method, closely integrating it with EMI prediction to establish a more comprehensive power device model validation framework.

- 5. Integration of Model-Based and Data-Driven Approaches: As demonstrated by Zhang et al. [40], combining model-based and data-driven methods for remaining useful life prediction of power MOSFETs provides improved accuracy and reliability. This hybrid approach represents a promising direction for enhancing both modeling accuracy and practical applicability.

These research directions will help improve the accuracy and practicality of power semiconductor device models, especially in system-level simulation and high-performance applications. graphicx

## **3 MOSFET and IGBT Model Correction and Analysis**

## 3.1 Overview of Semiconductor Device Modeling Methods and Research Data Sources and Experimental Design

Two main methodological schools have long existed in the field of power semiconductor device modeling: physics-oriented and mathematics-oriented approaches. These two methods have their own characteristics in model construction, parameter selection, and application scenarios, with far-reaching impacts on subsequent research.

The physics-oriented approach provides an intuitive conceptual model that corresponds directly to the physical structure of semiconductor devices. This method provides clear physical interpretations for each functional component, making the parameters easy to understand from a theoretical perspective, with predictable effects when adjusted. Each part of the equation represents a specific physical phenomenon within the device, such as the transfer characteristic function that simulates the control of the MOS channel, while the output characteristic function captures bipolar transistor behavior. This direct physical mapping makes the model particularly suitable for research and development work that requires in-depth understanding of the physics of the device and its working mechanisms.

In contrast, the mathematics-oriented approach, while more abstract in its conceptual model, establishes meaningful connections with physical characteristics through its hierarchical parameter structure. The physical meaning of parameters is more indirect, relying more on numerical fitting results and empirical knowledge. Parameter effects are more difficult to predict intuitively and require experience to interpret. However, this abstraction brings significant advantages in computational performance for complex systems. The relationship between mathematical formulas and device behavior is reflected through careful adjustment of parameters rather than explicit physical representation. This approach performs excellently in practical engineering applications, especially in cases where computational efficiency takes precedence over theoretical analysis, providing reliable performance in system-level simulation.

In terms of implementation complexity and software compatibility, physics-oriented equation implementation requires handling complex mathematical functions, with more cumbersome computational processes, and may require developers to custom-implement special functions, increasing the difficulty of cross-platform migration. Mathematical-oriented equations, on the other hand, rely only on basic mathematical operations, with standard support in all mainstream SPICE-type simulation tools, greatly reducing implementation difficulty and maintenance costs.

Convergence is a key factor in circuit simulation, directly affecting the reliability and computational efficiency of the results. The complex mathematical structure of physics-oriented equations, while accurately describing device behavior, may lead to a reduced convergence speed, especially with potential numerical instability in certain operating areas. Mathematical-oriented equations, with their concise mathematical structure, typically exhibit superior convergence properties, performing more robustly in complex system simulations. In practical applications, the ideal strategy often combines the strengths of both approaches: using mathematicsoriented equations for preliminary system design and large-scale simulation stages, and transitioning to physics-oriented equations for detailed analysis of key components and studies of extreme operating conditions. This chapter will systematically analyze the application of these two methods in MOSFET and IGBT modeling, exploring how to maintain the physical reasonableness of the model while improving its numerical efficiency and practicality.

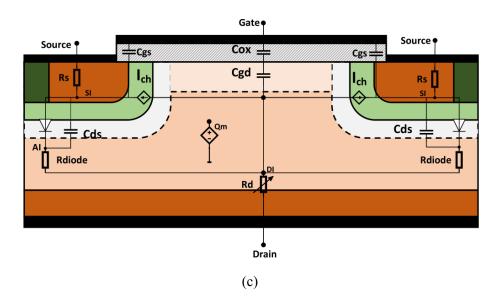

The objective of this research is to create accurate and portable wide-bandgap semiconductor SPICE behavioral models. The research data comes from two main sources: MOSFET data from WOLFSPEED's C2M0080120D device, and IGBT data based on simulated data points provided by TCAD physical models.

The WOLFSPEED C2M0080120D was chosen as the MOSFET research subject because it represents the main applications of modern wideband gap semiconductor technology, with typical characteristics and challenges. The experimental platform uses the open-source software LTspice, chosen based on two considerations: first, its open-source nature makes research results easily accessible; second, its compatibility allows models to be conveniently transferred to other SPICE software platforms, enhancing the application value of the research results.

Note that during the experiment, slight differences were found between the MOSFET device test results in the SPICE model and the datasheet. This difference may originate from system bias between WOLFSPEED's hardware testing equipment and SPICE simulation software. To ensure consistency and comparability of the research, this study chose the simulation results of the device model in SPICE as the benchmark comparison object, rather than directly using datasheet data.

For the IGBT modeling part, the research data comes from exact data points generated by TCAD (Technology Computer-Aided Design) physical models. These data points, calculated on the basis of semiconductor physical equations and detailed device structural parameters, have high physical accuracy and can reflect microscopic physical processes such as carrier distribution and electric field distribution within the IGBT. The data provided by TCAD models covers static characteristics under different gate voltages and collector voltages, providing a reliable foundation for developing high-precision IGBT behavioral models.

This dual source approach effectively eliminates systematic errors between different platforms, making the effects of model improvement more objective and credible, while also facilitating comparison of performance differences between MOSFET and IGBT under the same modeling method.

### 3.2 Static and Dynamic Modeling of Semiconductor Devices

#### 3.2.1 Static Part of Semiconductor Device Model

#### 3.2.1.1 Overview of Traditional IGBT Static Model

The IGBT (Insulated Gate Bipolar Transistor), as a key device in modern power electronic systems, requires precise modeling for system design and simulation. The traditional IGBT static model belongs to the mathematics-oriented approach inspired by physical properties, typically taking the following form:

$$I_{ST} = a - \frac{a}{1 + (V_{CE}/b)^c}$$

(3.1)

Where  $I_{ST}$  is the collector current,  $V_{CE}$  is the collector-emitter voltage, and the parameters a, b, and c are functions related to the gate voltage  $V_{GE}$ :

$$a = \frac{s1_a}{1 + ((V_{GE} - V_{th})/s2_a)^{s3_a}} + s4_a$$

(3.2)

$$b = \frac{s1_b}{1 + ((V_{GE} - V_{th})/s2_b)^{s3_b}} + s4_b$$

(3.3)

$$c = \frac{s1_c}{1 + ((V_{GE} - V_{th})/s2_c)^{s3_c}} + s4_c$$

(3.4)

This model form is concise and mathematically clear: parameter a represents the maximum current value, parameter b controls the position of the transition point from the linear region to the saturation region, and parameter c determines the steepness of the transition region. This model form originally originated from static modeling of MOSFETs and was later successfully applied to IGBTs, but still faces certain challenges in accurately fitting IGBT characteristics, especially the transition characteristics in the low  $V_{CE}$  region.

In circuit simulation environments, IGBTs are often implemented as hybrid equivalent circuits composed of N-channel MOSFETs and PNP bipolar transistors. This representation reflects the dual nature of the internal physical structure of IGBTs: the combination of MOS channel control and bipolar conduction mechanisms. In the low-voltage region, IGBT behavior is mainly influenced by channel formation and modulation, while in the high-voltage region it exhibits more characteristics of bipolar devices. This dual nature makes precise modeling of IGBTs more challenging than single devices. This is also the main reason why this model form faces challenges in accurately fitting transition characteristics in the low  $V_{CE}$  region.

In subsequent sections, we will propose an improved model that can more accurately describe the behavior of the transition region through corrections to transfer characteristics based on the traditional static model. This modification maintains the simplicity and physical meaning of the model while significantly improving its prediction accuracy in the low-voltage region.

#### 3.2.1.2 Transfer Characteristics and Output Characteristics Decomposition of Sechyp Model

In exploring more effective IGBT modeling methods, we were inspired by the MOSFET Sechyp model. The Sechyp model, which belongs to the physics-oriented approach, adopts a unique method: decomposing the device characteristics into the product of the transfer characteristics (F\_Trans) and the output characteristics (F\_Out).

The basic form of the Sechyp model is as follows:

$$I_{DS} = F_{Trans}(V_{GS}) \cdot F_{Out}(V_{DS})$$

(3.5)

Here  $F_{Trans}$  mainly describes the modulation effect of the gate voltage on current and  $F_{Out}$  describes the influence of drain voltage on current. This decomposition method provides a new perspective for understanding semiconductor device behavior, especially when analyzing transitional regions.

Further analyzing the traditional IGBT model  $I_{ST} = a - \frac{a}{1 + (V_{CE}/b)^c}$ , we can rewrite it as:

$$I_{ST} = a \cdot \left( 1 - \frac{1}{1 + (V_{CE}/b)^c} \right)$$

(3.6)

At first glance, this mathematical transformation seems to suggest that the parameter a corresponds to  $F_{Trans}(V_{GE})$ , and the expression  $\left(1 - \frac{1}{1 + (V_{CE}/b)^c}\right)$  corresponds to  $F_{Out}(V_{CE})$ . However, this simple correspondence has a key issue: in the traditional IGBT model, the parameters a, b, and c are all functions of  $V_{GE}$ , making the correspondence more complex.

In fact, a more accurate physical interpretation should be: parameter a mainly controls the current magnitude in the saturation region; From a physical meaning perspective, it is closer to the part describing output characteristics, that is, the maximum current the device can reach at a specific gate voltage; parameters band c control the transition characteristics from linear region to saturation region; from a physical meaning perspective, they are closer to transfer characteristics, as they describe how gate voltage modulates the channel.

Based on insights from the Sechyp model, we recognize that IGBT transfer characteristics should be influenced by both  $V_{GE}$  and  $V_{CE}$ . This means that to establish a more accurate IGBT model, the parameters b and c should not only be functions of  $V_{GE}$  but should also consider the influence of  $V_{CE}$ . Similarly, from a physical perspective, there exists a complex interaction between the gate voltage ( $V_{GE}$ ) and the collector voltage ( $V_{CE}$ ), especially in the transition region.

This understanding provides a new approach to develop improved IGBT models: By introducing corrections based on transfer characteristics in parameters b and c, while considering the interaction between  $V_{GE}$  and  $V_{CE}$ , we can more accurately capture the behavioral characteristics of IGBTs in the transition region. This approach is particularly suitable for IGBTs, as their composite structure and the presence of minority carriers make the interaction between gate control and collector voltage more significant.

#### 3.2.1.3 Analysis of Structural Differences Between IGBT and MOSFET

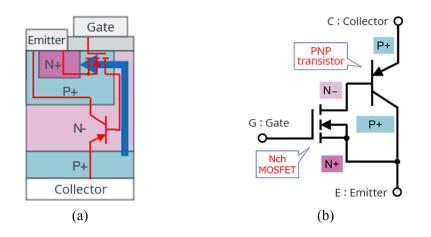

IGBT and MOSFET have fundamental differences in semiconductor physical structure, which directly affect their sensitivity to model corrections. As shown in Figure 3.1, the IGBT is essentially a composite structure of a MOSFET and a bipolar junction transistor (BJT), with an additional collector region P+, which introduces minority carrier injection mechanisms.

Structurally, MOSFETs adopt a four-layer structure (source metal-N+ source region-P body region-Ndrift region-N+ substrate-drain metal), while IGBTs adopt a five-layer structure (emitter metal-N+ emitter region-P body region-N-drift region-P+ collector region-collector metal). This additional P+ layer creates a PNP bipolar transistor structure, forming a composite working mechanism with the MOS control channel.

This structural difference leads to more complex transfer characteristics in IGBTs compared to MOSFETs, involving dual modulation mechanisms. MOS channel control (similarly to MOSFETs, the input part of

Figure 3.1: Comparison of IGBT and MOSFET structures. (a) The physical structure of IGBT. (b) The equivalent circuit of IGBT. (c) Cross-sectional structure of a MOSFET that relies solely on majority carrier conduction.

IGBTs is controlled by gate voltage to form channels, determining the switching state of the device) and bipolar injection effects (unlike MOSFETs, the output part of IGBTs includes a PNP structure, with the P+ collector region injecting minority carriers (holes) into the N-drift region, reducing on-resistance).

It is precisely this dual mechanism that gives IGBTs lower on-state voltage drop compared to MOSFETs in the conduction state, but also brings more complex current conduction and control characteristics. Our experimental results verified this: the same correction parameters can significantly improve the transition region fitting accuracy in IGBTs, while having a limited effect in MOSFETs. This indicates that the physical structure of IGBTs is more sensitive to transfer characteristic corrections, especially in the transition region.

IGBT and MOSFET have essential differences in carrier transport mechanisms, which is the key factor in their different responses to transfer characteristic corrections. There are significant differences in the flow path and the nature of the carriers in the two types of devices. MOSFETs are based solely on majority carriers (electrons) for conduction, and the type of carrier does not change as the current flows from the drain to the source. This single-carrier conduction mechanism makes its mathematical description relatively simple, with current-voltage characteristics mainly determined by channel electron concentration and mobility.

In contrast, IGBTs involve dual conduction of electrons and holes, forming complex carrier loops: electrons flow from the N+ emitter region into the inversion layer (channel) formed in the P body region; these electrons then continue flowing through the N-drift region to reach the P+ collector region, while the P+ collector region injects holes (minority carriers) into the N-drift region. Some of these injected holes flow towards the N+ emitter region through the P body region, while others recombine with electrons in the N-drift region, constituting the unique charge transport mechanism of IGBTs. In IGBTs, although the minority carriers (holes) injected from the P+ collector region are mainly controlled by  $V_{CE}$ , their distribution and effects in the drift region are influenced by the MOS channel electron flow (controlled by  $V_{GE}$ ), forming a typical "electron-hole plasma" region.

It should be noted that although minority carriers are mainly injected by drive  $V_{CE}$ , their presence significantly changes the distribution of the electric field and the distribution of conductivity within the device, thereby affecting the control efficiency of the gate in the channel. This influence is particularly significant in the low  $V_{CE}$  region: the injection and distribution of holes directly affect the electric field gradient, causing the transport characteristics of channel electrons to exhibit strong nonlinearity. This complex interaction makes it difficult to completely separate the "transfer characteristics" from the "output characteristics" in IGBTs, as there exists a strong coupling relationship between them. Therefore, corrections based on transfer characteristics can simultaneously affect multiple physical processes in IGBTs, producing more significant overall improvement effects.

IGBT and MOSFET also have significant differences in the conductivity modulation mechanisms, which further explains the different responses of the two devices to transfer characteristic corrections. There are essential differences in the conductivity formation and modulation processes of the two devices. In MOSFETs, conductivity is mainly directly controlled by the gate with a relatively simple mathematical expression:

$$G_{MOSFET} \approx \mu_n \cdot C_{ox} \cdot \frac{W}{L} \cdot (V_{GS} - V_{th})$$

(3.7)

Where  $\mu_n$  is the mobility of the electrons,  $C_{ox}$  is the capacitance of gate oxide, and W/L is the width to length ratio. This relationship indicates that MOSFET conductivity is mainly linearly modulated by gate-source voltage, with relatively simple channel formation and modulation processes.

In IGBT, the total conductivity consists of two parts:

$$G_{IGBT} \approx G_{MOS} + G_{drift}(n, p) \tag{3.8}$$

The MOS part ( $G_{MOS}$ ) is similar to the MOSFET conductivity, while the drift region conductivity ( $G_{drift}$ ) strongly depends on the concentration distribution of electrons and holes, exhibiting obvious nonlinear characteristics. Especially in the transition region, the injected holes significantly change the conductivity distribution in the drift region. This change in conductivity, in turn, affects the sensitivity of the channel current to  $V_{CE}$ , forming a complex feedback mechanism.

Based on the theoretical analysis presented above, we expect that the same transfer characteristic correction method will exhibit a significantly better performance improvement in IGBTs than in MOSFETs, especially in the low  $V_{CE}$  region. This is because: the composite structure of IGBTs makes the relationship between transfer characteristics and  $V_{CE}$  more nonlinear; the complex electric field distribution caused by minority carrier injection enhances parameter sensitivity; the dual conductivity modulation mechanism means that correction effects can simultaneously influence multiple physical processes. This theoretical expectation will be verified and quantitatively analyzed through detailed experimental results in Chapter 4.

#### 3.2.1.4 IGBT Model Correction Method Based on Transfer Characteristics

#### 3.2.1.4.1 Theoretical Basis of the Correction Method

Based on inspiration from the Sechyp model and analysis of IGBT physical characteristics, we propose a correction method based on transfer characteristics. The core concept of this method is: although the traditional model parameters b and c are formally functions of  $V_{GE}$ , their physical essence is closely related to the transfer characteristics and should consider the influence of both  $V_{GE}$  and  $V_{CE}$ .

From a physical perspective, IGBT behavior in the transition region is influenced by multiple factors: channel formation and modulation (as  $V_{CE}$  increases, the electric field near the channel end strengthens, causing the channel to gradually contract, directly affecting the control efficiency of the gate over the channel); minority carrier injection (although the minority carriers (holes) injected from the P+ collector region of the IGBT are mainly controlled by  $V_{CE}$ , their distribution in the drift region is influenced by the MOS channel electron flow (controlled by  $V_{GE}$ ), forming complex interactions); and nonlinear changes in conductivity (the conductivity in the transition region exhibits strong nonlinear characteristics, which are difficult to describe solely through  $V_{GE}$  or  $V_{CE}$ ). These physical phenomena indicate that, in the transition region, transfer characteristics have an inherent association with  $V_{CE}$ , requiring appropriate correction terms to capture this complex relationship.

#### 3.2.1.4.2 Design and Implementation of Correction Functions

Based on the theoretical analysis described above, we designed correction functions for the parameters b and c, and implemented a complete enhanced IGBT model. The complete implementation of the enhanced model includes three key correction parts:

(1) Exponential decay correction for parameter b

$$b\_correction = k_b \cdot \exp(-\alpha_b \cdot V_{CE}) \tag{3.9}$$

$$b = b \ original \cdot (1 + b \ correction) \tag{3.10}$$

The correction for parameter b adopts an exponential decay function with the following characteristics:

$$b\_correction = k_b \cdot \exp(-\alpha_b \cdot V_{CE}) \tag{3.11}$$

$$b = b \ original \cdot (1 + b \ correction) \tag{3.12}$$

The parameter b in the traditional model controls the position of the transition point from the linear region to the saturation region, corresponding to the modulation effect of the channel length. The exponential decay correction makes b significantly larger in the low  $V_{CE}$  region, consistent with the special physical behavior of channel formation in the low-voltage region. Using a multiplicative combination  $(1 + b_{correction})$  ensures that b always remains positive, avoiding numerical instability. At the same time, the multiplicative form makes the correction effect proportional to the original parameter, maintaining the physical continuity of the model. Through the parameters  $k_b$  (correction intensity) and  $\alpha_b$  (decay rate), the degree of influence of the correction in different  $V_{CE}$  regions can be precisely controlled.

(2) Correction of the S-shaped function for the parameter c

$$c\_correction = k_c \cdot \left(1 - \frac{1}{1 + \exp(-\alpha_c \cdot (V_{CE} - \beta_c))}\right)$$

(3.13)

$$c = c_{original} + c_{correction}$$

(3.14)